## PCN 18\_0020

# AD5671R/75R & AD5675 & AD5672R/76R & AD5676 Timing Specification Changes

This PCN convers data sheet timing specifications that will be changed from the released REV B AD5671R/75R & AD5675 & AD5672R/76R & AD5676 data sheets to the REV C AD5671R/75R & AD5675 & REV D AD5672R/76R & AD5676 data sheets. The old and new specifications are listed in the tables below.

# The Rev B AD5671R/75R & AD5675 timing specifications were:

### TIMING CHARACTERISTICS

$V_{DD}$  = 2.7 V to 5.5 V, 1.8 V  $\leq$  V<sub>LOGIC</sub>  $\leq$  5.5 V, all specifications -40°C to +125°C, unless otherwise noted.

| - <b>T</b> | - | ь1 | ~ | -  |

|------------|---|----|---|----|

| - 1        | a | DI | e | э. |

| Parameter <sup>1, 2</sup>   | Min                    | Max | Unit | Description                                                                             |

|-----------------------------|------------------------|-----|------|-----------------------------------------------------------------------------------------|

| t <sub>1</sub>              | 0.92                   |     | μs   | SCL cycle time                                                                          |

| t2                          | 0.11                   |     | μs   | tнісн, SCL high time                                                                    |

| t3                          | 0.44                   |     | μs   | t <sub>LOW</sub> , SCL low time                                                         |

| t4                          | 0.04                   |     | μs   | t <sub>HD,STA</sub> , start/repeated start hold time                                    |

| ts                          | 40                     |     | ns   | tsu,data setup time                                                                     |

| t6 <sup>3</sup>             | -0.04                  |     | μs   | t <sub>HD,DAT</sub> , data hold time                                                    |

| t7                          | -0.045                 |     | μs   | t <sub>SU,STA</sub> , repeated start setup time                                         |

| t <sub>8</sub>              | 0.195                  |     | μs   | t <sub>su,sto</sub> , stop condition setup time                                         |

| t9                          | 0.12                   |     | μs   | $t_{\mbox{\tiny BUF}}$ bus free time between a stop condition and a start condition     |

| t10 <sup>4</sup>            | 0                      |     | ns   | t <sub>R</sub> , rise time of SCL and SDA when receiving                                |

| t11 <sup>4,5</sup>          | 20 + 0.1C <sub>B</sub> |     | ns   | t <sub>F</sub> , fall time of SCL and SDA when transmitting/receiving                   |

| <b>t</b> 12                 | 20                     |     | ns   | LDAC pulse width                                                                        |

| t <sub>13</sub>             | 0.4                    |     | ns   | SCL rising edge to LDAC rising edge                                                     |

| t <sub>14</sub>             | 4.8                    |     | ns   | RESET minimum pulse width low, 1.8 V ≤ VLOGIC ≤ 2.7 V                                   |

|                             | 6.2                    |     | ns   | RESET minimum pulse width low, 2.7 V $\leq$ V <sub>LOGIC</sub> $\leq$ 5.5 V             |

| t <sub>15</sub>             | 132                    |     | ns   | $\overline{\text{RESET}}$ activation time, 1.8 V $\leq$ V <sub>LOGIC</sub> $\leq$ 2.7 V |

|                             | 80                     |     | ns   | $\overline{\text{RESET}}$ activation time, 2.7 V $\leq$ V <sub>LOGIC</sub> $\leq$ 5.5 V |

| t <sub>sp</sub> 6           | 0                      |     | ns   | Pulse width of suppressed spike                                                         |

| C <sub>B</sub> <sup>5</sup> |                        | 400 | pF   | Capacitive load for each bus line                                                       |

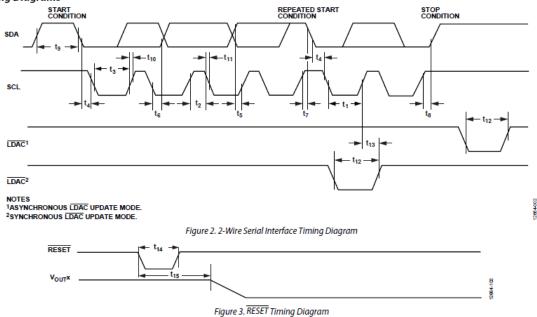

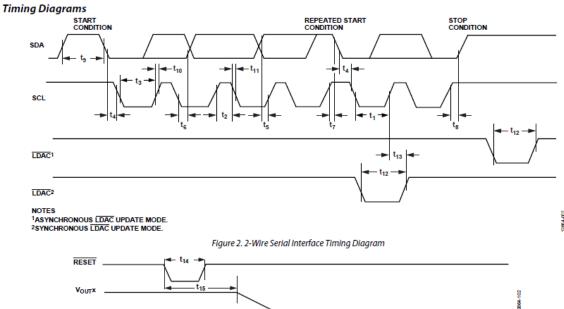

<sup>1</sup> See Figure 2.

<sup>2</sup> Guaranteed by design and characterization; not production tested.

<sup>3</sup> A master device must provide a hold time of at least 300 ns for the SDA signal (referred to the minimum V<sub>H</sub> of the SCL signal) to bridge the undefined region of the SCL falling edge.

$^4$  t\_R and t\_F are measured from 0.3  $\times$  V\_{DD} to 0.7  $\times$  V\_{DD}.

<sup>5</sup> Ca is the total capacitance of one bus line in pF. <sup>6</sup> Input filtering on the SCL and SDA inputs suppresses noise spikes that are less than 50 ns.

#### **Timing Diagrams**

# The Rev C AD5671R/75R & AD5675 timing specifications are:

### TIMING CHARACTERISTICS

$V_{DD}$  = 2.7 V to 5.5 V, 1.62 V  $\leq$  V<sub>LOGIC</sub>  $\leq$  5.5 V, all specifications -40°C to +125°C, unless otherwise noted.

| Parameter <sup>1</sup> | Min                    | Max | Unit | Description                                                                              |

|------------------------|------------------------|-----|------|------------------------------------------------------------------------------------------|

| t <sub>1</sub>         | 2.5                    | ·   | μs   | SCL cycle time                                                                           |

| t <sub>2</sub>         | 0.6                    |     | μs   | t <sub>HGH</sub> , SCL high time                                                         |

| t3                     | 1.3                    |     | μs   | tLOW, SCL low time                                                                       |

| t4                     | 0.6                    |     | μs   | t <sub>HD,STA</sub> , start/repeated start hold time                                     |

| ts                     | 100                    |     | ns   | t <sub>SU,DAT</sub> , data setup time                                                    |

| t6 <sup>2</sup>        | 0                      | 0.9 | μs   | thd,dat, data hold time                                                                  |

| t7                     | 0.6                    |     | μs   | t <sub>SU,STA</sub> , repeated start setup time                                          |

| t <sub>8</sub>         | 0.6                    |     | μs   | t <sub>SU,STO</sub> , stop condition setup time                                          |

| t9                     | 1.3                    |     | μs   | tsur, bus free time between a stop condition and a start condition                       |

| t10 <sup>3</sup>       | 0                      | 300 | ns   | t <sub>R</sub> , rise time of SCL and SDA when receiving                                 |

| t11 <sup>3</sup>       | 20 + 0.1C <sub>B</sub> | 300 | ns   | t <sub>F</sub> , fall time of SCL and SDA when transmitting/receiving                    |

| <b>t</b> 12            | 20                     |     | ns   | LDAC pulse width                                                                         |

| t <sub>13</sub>        | 400                    |     | ns   | SCL rising edge to LDAC rising edge                                                      |

| t14                    | 8                      |     | ns   | RESET minimum pulse width low, 1.62 V ≤ VLOGIC ≤ 2.7 V                                   |

|                        | 10                     |     | ns   | RESET minimum pulse width low, 2.7 V $\leq$ VLOGIC $\leq$ 5.5 V                          |

| t <sub>15</sub>        | 90                     |     | ns   | $\overline{\text{RESET}}$ activation time, 1.62 V $\leq$ V <sub>LOGIC</sub> $\leq$ 2.7 V |

|                        | 90                     |     | ns   | RESET activation time, 2.7 V $\leq$ VLOGIC $\leq$ 5.5 V                                  |

| t <sub>sp</sub> 4      | 0                      | 50  | ns   | Pulse width of suppressed spike                                                          |

| CB                     |                        | 400 | pF   | Capacitive load for each bus line                                                        |

<sup>1</sup> See Figure 2 and Figure 3.

<sup>3</sup> See Figure 2 and Figure 3.

<sup>2</sup> A master device must provide a hold time of at least 300 ns for the SDA signal (referred to the minimum V<sub>H</sub> of the SCL signal) to bridge the undefined region of the SCL falling edge.

<sup>3</sup> t<sub>R</sub> and t<sub>F</sub> are measured from 0.3 × V<sub>DD</sub> to 0.7 × V<sub>DD</sub>.

<sup>4</sup> Input filtering on the SCL and SDA inputs suppresses noise spikes that are less than 50 ns.

Figure 3. RESET Timing Diagram

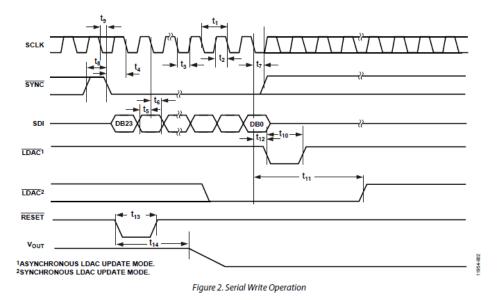

# The write timing specifications for the AD5672R/76R and AD5676 Rev. B were:

## TIMING CHARACTERISTICS

All input signals are specified with  $t_R = t_F = 1 \text{ ns/V}$  (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ . See Figure 2.  $V_{DD} = 2.7 \text{ V}$  to 5.5 V, 1.8 V  $\leq V_{LOGIC} \leq 5.5 \text{ V}$ , and  $V_{REFIN} = 2.5 \text{ V}$ . All specifications  $-40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted. Maximum SCLK frequency is 50 MHz at  $V_{DD} = 2.7 \text{ V}$  to 5.5 V, 1.8 V  $\leq V_{LOGIC} \leq V_{DD}$ . Guaranteed by design and characterization; not production tested.

|                 | $1.8 \text{ V} \le \text{V}_{\text{LOGIC}} < 2.7 \text{ V}$ | $2.7 \text{ V} \leq \text{V}_{\text{LOGIC}} \leq 5.5 \text{ V}$ |      |                                                                  |

|-----------------|-------------------------------------------------------------|-----------------------------------------------------------------|------|------------------------------------------------------------------|

| Parameter       | Min Max                                                     | Min Max                                                         | Unit | Description                                                      |

| t1              | 20                                                          | 20                                                              | ns   | SCLK Cycle Time                                                  |

| t <sub>2</sub>  | 4                                                           | 1.7                                                             | ns   | SCLK High Time                                                   |

| t3              | 4.5                                                         | 4.3                                                             | ns   | SCLK Low Time                                                    |

| t4              | 15.1                                                        | 10.1                                                            | ns   | SYNC to SCLK Falling Edge Setup Time                             |

| ts              | 0.8                                                         | 0.8                                                             | ns   | Data Setup Time                                                  |

| t <sub>6</sub>  | 0.1                                                         | -0.8                                                            | ns   | Data Hold Time                                                   |

| t7              | 0.95                                                        | 1.25                                                            | ns   | SCLK Falling Edge to SYNC Rising Edge                            |

| ts              | 9.65                                                        | 6.75                                                            | ns   | Minimum SYNC High Time (Single, Combined, or All Channel Update) |

| t9              | 4.75                                                        | 9.7                                                             | ns   | SYNC Falling Edge to SCLK Fall Ignore                            |

| t10             | 4.85                                                        | 5.45                                                            | ns   | LDAC Pulse Width Low                                             |

| t11             | 41.25                                                       | 25                                                              | ns   | SCLK Falling Edge to LDAC Rising Edge                            |

| t <sub>12</sub> | 26.35                                                       | 20.3                                                            | ns   | SCLK Falling Edge to LDAC Falling Edge                           |

| <b>t</b> 13     | 4.8                                                         | 6.2                                                             | ns   | RESET Minimum Pulse Width Low                                    |

| t <sub>14</sub> | 132                                                         | 80                                                              | ns   | RESET Pulse Activation Time                                      |

|                 | 5.15                                                        | 5.18                                                            | μs   | Power-Up Time <sup>1</sup>                                       |

<sup>1</sup> Time to exit power-down to normal mode of AD5672R/AD5676R operation, 32<sup>nd</sup> clock edge to 90% of DAC midscale value, with output unloaded.

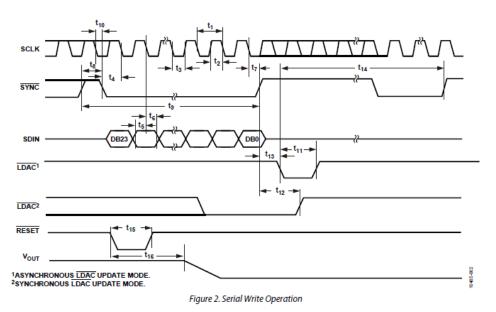

# The write timing specifications for the AD5672R/76R and AD5676 Rev. D are:

### TIMING CHARACTERISTICS

All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of ( $V_{IL} + V_{IH}$ )/2. See Figure 2.  $V_{DD} = 2.7$  V to 5.5 V, 1.62 V  $\leq V_{LOGIC} \leq$  5.5 V;  $V_{REFIN} = 2.5$  V. All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| -  |   |     | _  |

|----|---|-----|----|

| Ta | ы | 0   | 5  |

| ы  | U | IC. | э. |

|    |   |     |    |

|                                                             |                 | 1.62 V ≤ VLOGIC < 2.7 | V 2.7V≤V | $2.7~V \leq V_{\text{LOGIC}} \leq 5.5~V$ |      |

|-------------------------------------------------------------|-----------------|-----------------------|----------|------------------------------------------|------|

| Parameter                                                   | Symbol          | Min Max               | x Min    | Max                                      | Unit |

| SCLK Cycle Time                                             | t <sub>1</sub>  | 20                    | 20       |                                          | ns   |

| SCLK High Time                                              | t <sub>2</sub>  | 8                     | 8        |                                          | ns   |

| SCLK Low Time                                               | t <sub>3</sub>  | 10                    | 12       |                                          | ns   |

| SYNC to SCLK Falling Edge Setup Time                        | t4              | 15                    | 11       |                                          | ns   |

| Data Setup Time                                             | ts              | 2                     | 3        |                                          | ns   |

| Data Hold Time                                              | t <sub>6</sub>  | 2                     | 2        |                                          | ns   |

| SCLK Falling Edge to SYNC Rising Edge                       | t7              | 4                     | 4        |                                          | ns   |

| Minimum SYNC High Time                                      | t <sub>8</sub>  | 15                    | 12       |                                          | ns   |

| SYNC Rising Edge to SYNC Rising Edge (DAC Register Updates) | t9              | 870                   | 830      |                                          | ns   |

| SYNC Falling Edge to SCLK Fall Ignore                       | <b>t</b> 10     | 4                     | 4        |                                          | ns   |

| LDAC Pulse Width Low                                        | t11             | 8                     | 8        |                                          | ns   |

| SYNC Rising Edge to LDAC Rising Edge                        | t <sub>12</sub> | 25                    | 25       |                                          | ns   |

| SYNC Rising Edge to LDAC Falling Edge                       | t <sub>13</sub> | 25                    | 25       |                                          | ns   |

| LDAC Falling Edge to SYNC Rising Edge                       | <b>t</b> 14     | 840                   | 800      |                                          | ns   |

| Minimum Pulse Width Low                                     | t15             | 8                     | 10       |                                          | ns   |

| RESETActivation Time                                        | t <sub>16</sub> | 90                    | 90       |                                          | ns   |

| Power-Up Time <sup>1</sup>                                  |                 | 5.5                   | 5.5      |                                          | μs   |

|                                                             |                 |                       |          |                                          |      |

<sup>1</sup> Time to exit power-down to normal mode of AD5672R/AD5676R operation, SYNC rising edge to 90% of DAC midscale value, with output unloaded.

# The daisy-chain and readback timing specifications for the AD5672R/76R and AD5676 Rev. B were:

## DAISY-CHAIN AND READBACK TIMING CHARACTERISTICS

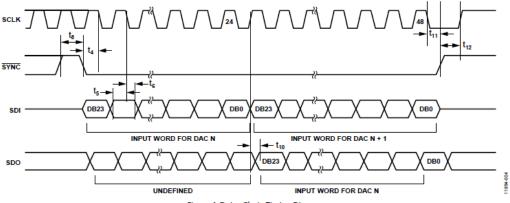

All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of ( $V_{IL} + V_{IH}$ )/2. See Figure 4 and Figure 5.  $V_{DD} = 2.7$  V to 5.5 V, 1.8 V  $\leq V_{LOGIC} \leq 5.5$  V,  $V_{REF} = 2.5$  V. All specifications –40°C to +125°C, unless otherwise noted. Maximum SCLK frequency is 25 MHz or 15 MHz at  $V_{DD} = 2.7$  V to 5.5 V, 1.8 V  $\leq V_{LOGIC} \leq V_{DD}$ . Guaranteed by design and characterization; not production tested.

|                 | 1.8 V | $1.8 \text{ V} \leq \text{VLOGIC} < 2.7 \text{ V} \qquad 2.7 \text{ V} \leq \text{VLOGIC} \leq 5.5 \text{ V}$ |      |     |      |                                       |

|-----------------|-------|---------------------------------------------------------------------------------------------------------------|------|-----|------|---------------------------------------|

| Parameter       | Min   | Max                                                                                                           | Min  | Max | Unit | Description                           |

| tı .            | 120   | ·                                                                                                             | 83.3 |     | ns   | SCLK Cycle Time                       |

| t <sub>2</sub>  | 33    |                                                                                                               | 25.3 |     | ns   | SCLK High Time                        |

| t₃              | 2.8   |                                                                                                               | 3.25 |     | ns   | SCLK Low Time                         |

| t₄              | 75    |                                                                                                               | 50   |     | ns   | SYNC to SCLK Falling Edge             |

| t₅              | 1.2   |                                                                                                               | 0.5  |     | ns   | Data Setup Time                       |

| t <sub>6</sub>  | 0.3   |                                                                                                               | 0.4  |     | ns   | Data Hold Time                        |

| t7              | 16.2  |                                                                                                               | 13   |     | ns   | SCLK Falling Edge to SYNC Rising Edge |

| t <sub>8</sub>  | 55.1  |                                                                                                               | 45   |     | ns   | Minimum SYNC High Time                |

| t <sub>10</sub> | 21.5  |                                                                                                               | 22.7 |     | ns   | SDO Data Valid from SCLK Rising Edge  |

| t11             | 24.4  |                                                                                                               | 20.3 |     | ns   | SCLK Falling Edge to SYNC Rising Edge |

| t <sub>12</sub> | 85.5  |                                                                                                               | 54   |     | ns   | SYNC Rising Edge to SCLK Rising Edge  |

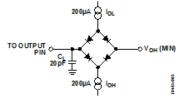

### Circuit Diagram and Daisy-Chain and Readback Timing Diagrams

Figure 3. Load Circuit for Digital Output (SDO) Timing Specifications

Figure 4. Daisy-Chain Timing Diagram

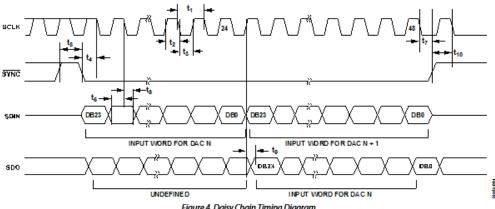

# The daisy-chain and readback timing specifications for the AD5672R/76R and AD5676 Rev. D are:

## DAISY-CHAIN AND READBACK TIMING CHARACTERISTICS

All input signals are specified with  $t_{g_{L}} = t_{E} = 1$  ns/V (10% to 90% of V<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>)/2. See Figure 4 and Figure 5.  $V_{DD}$  = 2.7 V to 5.5 V, 1.62 V  $\leq$   $V_{LOGHC}$   $\leq$  5.5 V;  $V_{REF}$  = 2.5 V. All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.  $V_{DD}$  = 2.7 V to 5.6 V, 1.62 V  $\leq$   $V_{LOGHC}$   $\leq$  5.5 V;  $V_{REF}$  = 2.5 V. All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.  $V_{DD}$  = 2.7 V to 5.6 V, 1.62 V  $\leq$   $V_{LOGHC}$   $\leq$  5.5 V;  $V_{REF}$  = 2.5 V. All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.  $V_{DD}$  = 2.7 V to 5.6 V;  $V_{REF}$  = 2.5 V. All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. to 5.5 V.

#### Table 5.

|                                       |                | 1.62 | V≤V <sub>LOGIC</sub> < 2.7 V | 2.7 | $2.7 V \le V_{LOGIC} \le 5.5 V$ |      |

|---------------------------------------|----------------|------|------------------------------|-----|---------------------------------|------|

| Parameter                             | Symbol         | Min  | Max                          | Min | Max                             | Unit |

| SCLK Cycle Time                       | t1             | 130  |                              | 110 |                                 | ns   |

| SCLK High Time                        | t2             | 33   |                              | 23  |                                 | ns   |

| SCLK Low Time                         | t3             | 12   |                              | 7   |                                 | ns   |

| SYNC to SCLK Falling Edge             | t,             | 80   |                              | 80  |                                 | ns   |

| Data Setup Time                       | ts             | 2    |                              | 2   |                                 | ns   |

| Data Hold Time                        | t <sub>6</sub> | 2    |                              | 2   |                                 | ns   |

| SCLK Falling Edge to SYNC Rising Edge | t7             | 35   |                              | 10  |                                 | ns   |

| Minimum SYNC High Time                | t <sub>8</sub> | 55   |                              | 30  |                                 | ns   |

| SDO Data Valid from SCLK Rising Edge  | t9             | 60   |                              | 50  |                                 | ns   |

| SYNC Rising Edge to SCLK Falling Edge | t10            | 2    |                              | 6   |                                 | ns   |

| SYNC Rising Edge to SDO Disable       | t11            | 40   |                              | 35  |                                 | ns   |

#### **Circuit and Timing Diagrams**

Figure 3. Load Circuit for Digital Output (SDO) Timing Specifications

Figure 4. Daisy Chain Timing Diagram